## BỘ GIÁO DỤC VÀ ĐÀO TẠO TRƯỜNG ĐẠI HỌC SỬ PHẠM KỸ THUẬT THÀNH PHỐ HỎ CHÍ MINH

#### TRẦN VĨNH THANH

# NGHIÊN CỬU BỘ NGHỊCH LƯU TĂNG ÁP BA BẬC HÌNH T TRONG TRẠNG THÁI BÌNH THƯỜNG VÀ SỰ CỐ HỞ MẠCH KHÓA CÔNG SUẤT

DANH MỤC CÁC BÀI BÁO ĐÃ CÔNG BỐ

Tp. Hồ Chí Minh, tháng năm 2023

# BỘ GIÁO DỤC VÀ ĐÀO TẠO TRƯỜNG ĐẠI HỌC SƯ PHẠM KỸ THUẬT THÀNH PHỐ HỎ CHÍ MINH

#### TRẦN VĨNH THANH

# NGHIÊN CỬU BỘ NGHỊCH LƯU TĂNG ÁP BA BẬC HÌNH T TRONG TRẠNG THÁI BÌNH THƯỜNG VÀ SỰ CỐ HỞ MẠCH KHÓA CÔNG SUẤT

NGÀNH: KỸ THUẬT ĐIỆN TỬ - 9520203

| Người | hưởng | dan | khoa | học: | TS. | Nguyêr | ı Mınh | Khai |

|-------|-------|-----|------|------|-----|--------|--------|------|

|       |       |     |      |      |     |        |        |      |

|       |       |     |      |      |     |        |        |      |

Phản biện 1:

Phản biện 2:

Phản biện 3:

Tp. Hồ Chí Minh, tháng năm 2023

### CÁC CÔNG TRÌNH ĐÃ CÔNG BỐ

- [1] D. -T. Do, V. -T. Tran, M. -K. Nguyen and S. Naik, "Fault Tolerant Control Methods for Three-Level Boost T-Type Inverter," *IEEE Transactions on Industrial Electronics*, 2022.

- [2] Duc-Tri Do, Vinh-Thanh Tran, Minh-Khai Nguyen. An DPWM for Active DC-Link Type Quasi-Z-Source Inverter to Reduce Component Voltage Rating. *Energies*, vol. 15, no. 13, pp. 4889, July 2022.

- [3] V. -T. Tran, M. -K. Nguyen, D. -T. Do and Y. -O. Choi, "Space Vector Modulation Method-Based Common Mode Voltage Reduction for Active Impedance-Source T-Type Inverter," *IEEE Access*, vol. 10, pp. 10149-10159, 2022.

- [4] Duc-Tri Do, Vinh-Thanh Tran, Minh-Khai Nguyen. Enhanced Boost Factor for Three-Level Quasi-Switched Boost T-Type Inverter. *Energies*, vol. 14, no. 13, pp. 3920, May 2021.

- [5] V. -T. Tran, M. -K. Nguyen, D. -T. Do and D. Vinnikov, "An SVM Scheme for Three-Level Quasi-Switched Boost T-Type Inverter With Enhanced Voltage Gain and Capacitor Voltage Balance," *IEEE Transactions on Power Electronics*, vol. 36, no. 10, pp. 11499-11508, Oct. 2021.

11

12

13

15

17

18

19

20

21

22

24

25

26

27

28

29

30

31

32

33

34

35

37

38

1

41

42

43

45

49

50

52

53

55

56

57

59

63

67

70

71

72

78

79

81

# Fault Tolerant Control Methods for Three-Level Boost T-Type Inverter

Duc-Tri Do , Vinh-Thanh Tran, Minh-Khai Nguyen , Senior Member, IEEE, and Sanjeev M. Naik, Senior Member, IEEE

Abstract—This article presents control techniques for three-level boost T-type inverter (TLB-T2I) to address opencircuit faults (OCFs) and short-circuit faults (SCFs) of semiconductor devices. Three main groups of semiconductor failures of TLB-T<sup>2</sup>I are OCFs of boost switches (F1), OCFs of inverter half bridge switches (F2), and OCFs of bidirectional switches (F3). Under the proposed approaches, the inverter generates a two-level output voltage with the F1 and F2 faults, while it still generates a three-level output voltage with the F3 fault. These control techniques are extended to solve OCF and SCF of diodes, SCF of boost switches, and OCF of capacitors. Operating modes of the inverter in both normal and fault conditions are presented. Design guidelines, power loss contribution, and comparison study are included. The experimental results based on a 1-kVA prototype are carried out to verify the accuracy of the proposed methods. The result shows that the proposed methods can reduce component voltage ratings when compared to the conventional methods. In particular, the voltage rating of the inverter half-bridge switch in the F2 fault-tolerant method is reduced by at least 50% compared to the traditional techniques.

Index Terms—Fault-tolerant (FT), open-circuit fault (OCF), space-vector modulation, three-level boost (TLB) inverter, t-type inverter.

#### I. INTRODUCTION

N RECENT years, inverters based on fast semiconductor devices have provided good performance because of their advantages, such as high-power density, high efficiency, and good output power quality [1]. However, these power switching devices have a high failure rate. Solving semiconductor failure can improve the system reliability, especially in some applications as an uninterruptable power supply. Semiconductor failures can be classified into two main groups: open-circuit fault (OCF) and short-circuit fault (SCF). The reasons for these failures are

Manuscript received 9 February 2022; revised 14 May 2022 and 30 June 2022; accepted 22 July 2022. This work was supported by T2021-43TĐ project. (Corresponding author: Minh-Khai Nguyen.)

Due-Tri Do and Vinh-Thanh Tran are with the Faculty of Electrical and Electronics Engineering, Ho Chi Minh City University of Technology and Education, Ho Chi Minh City 700000, Vietnam (e-mail: tridd@hcmute.edu.vn; thanhtv.ncs@hcmute.edu.vn).

Minh-Khai Nguyen and Sanjeev M. Naik are with the General Motor, Warren, MI 48092 USA (e-mail: minh-khai.nguyen@gm.com; sanjeev. m.naik@gm.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TIE.2022.3196341.

Digital Object Identifier 10.1109/TIE.2022.3196341

discussed in [2]–[4]. In general, the SCF is more serious than the OCF and usually leads to destroy the system due to the high short-circuit current. Then, the system is usually forced to stop for safety whenever SCF is detected. An impedance-source network can be installed before a conventional voltage source inverter to limit the amplitude of SC current [5]–[7]. It gives the system more time to handle the SCF. In contrast to the SCF, the inverter can keep operating by using appropriate modulation techniques when the OCF occurs. Thus, the solving OCF problem has attracted many researchers. Many studies about OCF diagnosis [8]–[11] and fault-tolerant (FT) methods [12]–[31] have been proposed. These methods provide many fast and exact detection methods for the OCF. Especially, the work in [8] can detect the OCF within 10  $\mu$ s.

The FT methods for OCF are usually applied to multilevel inverters [12]–[34]. A seven-level cascaded H-bridge inverter with fault tolerant capability is introduced in [12]. In this article, the faulty H-bridge is bypassed to isolate failed semiconductor devices. Active switches are installed at the output terminals of the H-bridge circuit to make short circuit the output voltage of faulty submodule. As a result, the amplitude of output voltage is decreased in post-fault operation. Besides the cascaded topology, T-type inverter topology is an attractive structure for implementing FT methods [13], [14]. However, the magnitude of the output voltage is also reduced when the FT scheme is activated [13], [14].

The conventional three-level T-type inverter with FT capability has received a lot of attention from researchers. In this topology, a single OCF can occur at either upper, lower, or bidirectional switches. The OCF of the bidirectional switch produces not only a small degradation of the output current quality but also unbalanced capacitor voltages. This OCF can be easily addressed by modifying the modulation schemes [15]–[17]. In these studies, the faulty phase operates as a two-level inverter with the help of upper and lower switches, while the other healthy phases operate as in normal condition. In particular, the methods in [15] and [16] provided capacitor voltage balancing under fault condition. When the OCF occurs at the upper or lower switch of the T-type inverter, the positive or negative half cycle of output current is not achieved. It generates a serious distortion at the output current. The system must be stopped if the FT solution is not applied. Two main solutions for the case of OCF include using additional hardware circuits [18]–[27] and appropriate pulsewidth modulation (PWM) techniques [26]-[31]. The simplest way to recover inverter operation in single

Q2

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104 105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

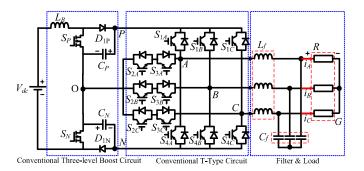

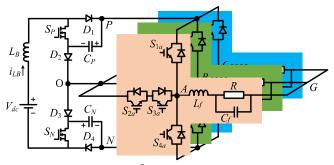

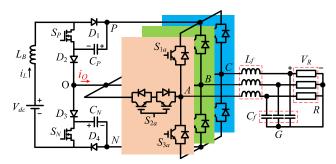

Fig. 1. Topology of conventional TLB-T<sup>2</sup>I [32].

or multiple semiconductor OCFs is to use two parallel inverters [18]–[21]. However, this solution requires a large number of switching devices. Another solution is to use an additional inverter redundant leg as presented in [22]–[25]. In [22] and [23], one extra T-type branch was installed before the main T-type inverter. The bidirectional switch of redundant leg was always turned ON to connect the dc-link mid-point to the main inverter in normal condition. In post-fault operation, this bidirectional switch is turned OFF to isolate the main circuit from the neutral point. Then, the inverter operates as a two-level inverter. The bidirectional switches of the main T-type circuit and upper or lower switches of the redundant leg help to continuously provide energy to the load. The works in [24] and [25] introduced a novel redundant leg consisting of two active switches and six diodes. The main T-type circuit of this solution was also modified, which used six extra diodes for inner switches. In post-fault operation, this inverter also produces a two-level voltage at output terminals. In general, the hardware-based solution brings many benefits such as ensuring full output power rating and solving multiple OCFs. However, it requires many additional semiconductor devices as well as the inverter only operates in buck mode.

The other solutions in [26]–[29] are based on PWM control techniques. In the reports in [26] and [27], bidirectional switches of faulty phase are turned ON to clamp the output terminal to the mid-point of input voltage. The other healthy phases with modified modulation signals help to recover output voltages. The study in [28] used inner and lower switches to solve the OCF of upper switches. In [28], the inverter operation degrades from three levels down to two levels. These methods do not require any extra semiconductor devices. However, in [26]–[28], the amplitude of the output voltage is reduced by half compared to the normal condition. To ensure desired output voltage, a dc-dc boost converter should be installed before the inverter to boost the dc-link voltage. For example, the 3L-T<sup>2</sup>I following a three-level boost (TLB) converter [32] as shown in Fig. 1 can be used to apply the FT method in [26]-[28] with no output voltage degrading. Besides the conventional two-stage inverter, an impedance-source network can be used before the conventional multilevel inverter [29]–[31]. The configurations in [29]–[31] provide buck-boost operation in single-stage power conversion, allowing for the compensation of output voltage degradation in postfault operation by boosting the dc-link voltage. Especially,

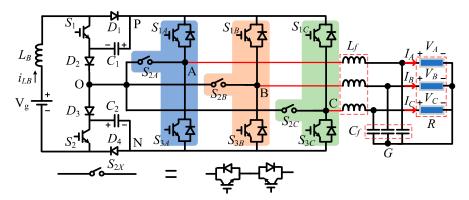

Fig. 2. Topology of TLB-T<sup>2</sup>I.

the work in [31] provides a full OCF solution for all active switches with smaller component voltage stress compared to that in [29] and [30].

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

160

161

162

163

164

165

166

167

The single-stage inverters in [29]–[31] require a very high dc-link voltage to generate a desired output voltage, which increases component voltage rating, especially for the upper and lower switches of the T-type circuit. Furthermore, the OCF and SCF that occurs at semiconductor devices of the impedance-source network are not considered in [29]–[31]. The conventional solution for OCF of upper or lower switch in [26] and [29]–[31] is not able to address the OCF of multiple upper or lower switches.

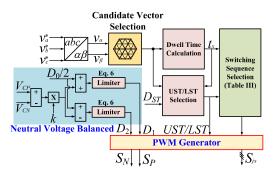

This article introduces some control techniques for TLB T-type inverter (TLB-T<sup>2</sup>I) to solve existing drawbacks of solutions in [26]–[31]. The rest of this article consists of six sections. Sections II and III present PWM schemes for TLB-T<sup>2</sup>I in normal and post-fault operation. Design guidelines and power loss calculations are included in Section IV. Some comparisons of component voltage stress between the proposed method and prior methods are shown in Section V. The experimental results and conclusion are attached in Sections VI and VII, respectively.

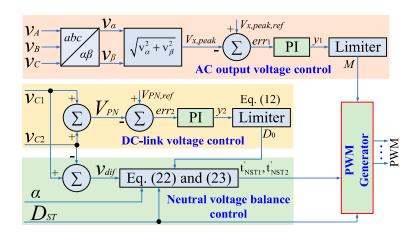

#### II. OPERATING OF TLB-T2I IN NORMAL CONDITION

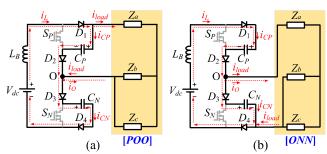

The configuration of TLB-T<sup>2</sup>I shown in Fig. 2 consists of a boost network and a conventional 3L-T<sup>2</sup>I, followed by a three-phase low-pass LC filter and output resistive load. The TLB circuit includes a boost inductor  $L_B$ , two capacitors  $C_P$  and  $C_N$ , two switches  $S_P$  and  $S_N$ , and four diodes  $D_1 - D_4$ . Compared to the conventional TLB shown in Fig. 1, this topology uses two more diodes,  $D_2$  and  $D_3$ . These extra diodes help to immune shoot-through state in the inverter side circuit. As a result, this configuration can limit the SC current generated when SCF of the inverter side switch occurs. The 3L-T<sup>2</sup>I ensures a three-level voltage at output pole voltage  $V_{XO}$  (X = A, B, C), which are denoted as states [P], [O], and [N]. The switching states of 3L-T<sup>2</sup>I are like those of a conventional voltage-source inverter, which is given in Table I. In normal condition, the TLB-T<sup>2</sup>I is introduced to work as a two-stage inverter. The dc-link voltage,  $V_{PN}$ , is controlled by two switches  $S_P$  and  $S_N$ . The interleaved control for both switches  $S_P$  and  $S_N$  to reduce inductor current ripple can be found in [33]. The capacitor voltages can be calculated as [33]

$$V_{CP} = V_{CN} = V_{dc}/[2(1-D)]$$

(1)

TABLE I on/off STATES OF 3L-T<sup>2</sup>I (X = A, B, C)

| State | ON Switch           | $V_{XO}$    |

|-------|---------------------|-------------|

| [P]   | $S_{1X}$ , $S_{2X}$ | $+V_{PN}/2$ |

| [O]   | $S_{2X}$ , $S_{3X}$ | 0           |

| [N]   | $S_{3X}$ , $S_{4X}$ | $-V_{PN}/2$ |

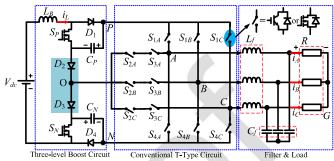

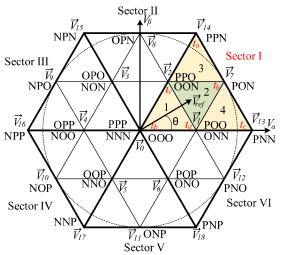

Fig. 3. Space vector diagram of proposed  $S_P$  OC FT method.

where *D* is the duty ratio of switches  $S_P$  and  $S_N$  (D < 1).

The inverter side is controlled by the conventional space vector modulation (SVM) method [34]. In this scheme, the peak-value of output phase voltage  $(V_{x,peak})$  is expressed as

$$V_{x,\text{peak}} = 2/\sqrt{3}MV_{PN}/2 = 1/\sqrt{3}MV_{dc}/(1-D)$$

(2)

where M is modulation index  $(M \le 1)$ ;  $V_{PN}$  is dc-link voltage. The voltage gain, G, of the inverter is calculated as

$$G = V_{x,\text{peak}}/(V_{\text{dc}}/2) = 2/\sqrt{3} \times M/(1-D).$$

(3)

#### III. FAULT-TOLERANT METHODS FOR TLB-T21

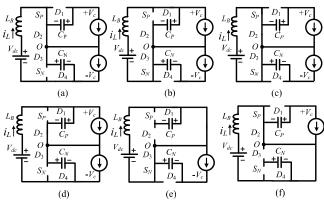

A single OCF is considered in this section. The failure is divided into two cases: a failure of the boost side switch, and a failure of the inverter side switch. The OCFs at the inverter circuit are divided into two groups: the OCF at upper switch  $S_{1X}$  or lower switch  $S_{4X}$  (X = A, B, and C) and the OCF at bidirectional switches  $S_{2X}$  and  $S_{3X}$ . Because of symmetry, only OCF at  $S_P$ , OCFs at  $S_{1A}$  and bidirectional switch fault at  $S_{2A}$  and  $S_{3A}$  are considered.

#### A. FT for OCF at $S_P$

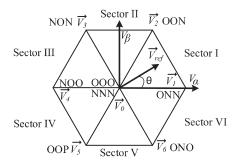

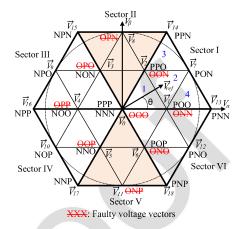

Assume that the OCF occurs at switch  $S_P$ . The capacitor  $C_N$  voltage is decreased while the capacitor  $C_P$  voltage is increased. The neutral voltage is unbalanced, which generates distortion at the output voltages. This OCF can be addressed by working as a two-stage two-level inverter with the modified space vector diagram shown in Fig. 3.

In proposed method, the inverter side produces two states at output voltage,  $V_{XO}$ , as [O] and [N]. State [O] denotes that  $V_{XO}$  is zero, which is generated by activating both switches  $S_{2X}$  and  $S_{3X}$ . While state [N] represents that  $V_{XO}$  is  $-V_{CN}$ , which is ensured by turning ON both  $S_{3X}$  and  $S_{4X}$ . In postfault operation, switch  $S_{3X}$  is always turned ON. The switching state combinations are shown in Fig. 3. The state [NNN] generated by activating switches  $S_{4A}$ ,  $S_{4B}$ , and  $S_{4C}$  is not utilized.

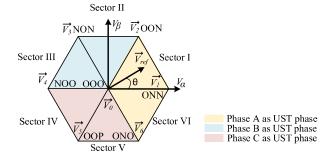

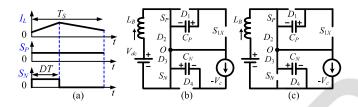

Fig. 4. (a) Control signals of switch  $S_N$ , and operating modes to tolerate  $S_P$  OCF. (b) Mode 1. (c) Mode 2.

In general, sector I is considered as an example for analysis. Three voltage vectors  $\vec{V}_0$ ,  $\vec{V}_1$ , and  $\vec{V}_2$  are adopted to generate reference vector  $\vec{V}_{\rm ref}$ . The relationship between these voltage vectors is shown as

$$\begin{cases} \vec{V}_{\text{ref}} \cdot T_s = \vec{V}_0 \cdot t_0 + \vec{V}_1 \cdot t_1 + \vec{V}_2 \cdot t_2 \\ T_s = t_0 + t_1 + t_2 \end{cases}$$

(4)

where  $T_s$  is the sampling period; and  $t_0$ ,  $t_1$ , and  $t_2$  are on-times of vectors  $\vec{V}_0$ ,  $\vec{V}_1$ , and  $\vec{V}_2$ , respectively.

Vectors  $\vec{V}_0$ ,  $\vec{V}_1$  , and  $\vec{V}_2$  are defined as

$$\begin{cases} \vec{V}_{\text{ref}} = 1/\sqrt{3}.M.V_{CN}.e^{j\theta} \\ \vec{V}_{0} = 0 \\ \vec{V}_{1} = 2/3.V_{CN}.e^{j0} \\ \vec{V}_{2} = 2/3.V_{CN}.e^{j\pi/3} \end{cases}$$

(5)

By substituting (5) into (4), the dwell-times of these candidate voltage vectors can be identified as

$$\begin{cases} t_1 = MT_s \sin(\pi/3 - \theta) \\ t_2 = MT_s \sin(\theta) \\ t_0 = T_s - t_1 - t_2 \end{cases}$$

(6)

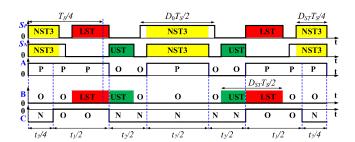

The switching sequence of the sector I is [OOO]-[OON]-[ONN]-[OON]-[OOO]. In this sector, phase A always produces state [O] at the output side. Thus, to boost the  $C_N$  voltage, this method inserts the upper-shoot-through (UST) state into phase A to generate modes 1 and 2 shown in Fig. 4. In these modes, switches  $S_{1A}$ ,  $S_{2A}$ , and  $S_{3A}$  are simultaneously turned ON, while diode  $D_2$  is reverse-biased. Note that this insertion still generates state [O] at  $V_{AO}$ . The result is that capacitor  $C_P$  is disconnected from the main circuit, and two-level operation of the inverter is ensured by capacitor  $C_N$ .

The boost operation is ensured by controlling the duty cycle of switch  $S_N$ . The control signal of  $S_N$  is shown in Fig. 4(a). When switch  $S_N$  is turned ON, inductor  $L_B$  stores energy from the dc input source. When switch  $S_N$  is triggered OFF, the inductor voltage and input source charge for the capacitor  $C_N$ . The voltage across capacitor  $C_N$  can be calculated as

$$V_{CN} = V_{dc}/(1-D).$$

(7)

The  $C_N$  voltage is twice that in normal condition for the same duty ratio, D, which ensures desired amplitude of output voltage, as shown in (8). The voltage gain is kept as (3)

$$V_{x,\text{peak}} = 2/\sqrt{3} \times M \times V_{CN}/2 = 1/\sqrt{3} \times M \times V_{\text{dc}}/(1-D).$$

Fig. 5. Space vector diagram of proposed method for  $S_{1A}$  OC FT.

Fig. 6. (a) Control signals of switches  $S_P$  and  $S_N$ , and operating modes to tolerate  $S_{1\,A}$  OCF. (b) Mode 1. (c) Mode 2.

#### B. OCF at $S_{1A}$

Under OCF of  $S_{1A}$ , the output voltage  $V_{AO}$  cannot obtain the state [P]. This fault distorts the output voltage because the positive half cycle cannot be achieved. As a result, two capacitor voltages are seriously unbalanced. Similar to the OCF at  $S_P$ , the OCF at  $S_{1A}$  can be solved by applying a two-stage two-level control method. Under the proposed scheme, switch  $S_P$  is always triggered on, which reverses biased diode  $D_1$ , as shown in Fig. 6. Two states [O] and [N] at output pole voltage,  $V_{XO}$ , are generated by the same way as FT method for  $S_P$  OCF. Switches  $S_{1B}$  and  $S_{1,C}$  are always triggered OFF in postfault operation of  $S_{1,A}$  OCF. The operating of inverter side is the same as a conventional two-level inverter, which depends on the location of the reference vector  $\vec{V}_{\text{ref}}$ . For example, when the reference vector, as shown in Fig. 5, falls in sector I, the switching sequence is [OOO]-[OON]-[ONN]-[NNN]-[ONN]-[OON]-[OOO]. The dwell-time calculation is detailed in (4)–(6). Unlike FT method for the OCF at  $S_P$ , vector [NNN] is also used in the case of  $S_{1A}$  OCF. The boost operation is also achieved by adjusting the duty ratio D, of switch  $S_N$ , as shown in Fig. 6(a). The voltage across capacitor  $C_N$  and output voltage are also expressed as (7) and (8).

#### C. OCF at $S_{2A}$ and $S_{3A}$

The OCF of  $S_{2A}$  and  $S_{3A}$  is not important when compared with OCF of  $S_P$  and  $S_{1A}$ . Output voltage  $V_{AO}$  cannot reach state [O] under  $S_{2A}$  and  $S_{3A}$  OCF conditions. This causes a slight total harmonic distortion (THD) increment at the output voltage and unbalanced capacitor voltages.

To solve this OCF, in sectors I–VI, the operation of the inverter can be guaranteed by using the redundant voltage vectors. For example, assuming that the reference vector is located in region 2 of sector I, as shown in Fig. 7. In normal condition,

Fig. 7. Space vector diagram to solve bidirectional switch OCF.

the switching sequence is [PPO]-[POO]-[PON]-[OON]-[ONN] and return. When OCFs at  $S_{2A}$  and  $S_{3A}$  occur, vectors [OON] and [ONN] cannot be reached. Thus, small vectors [PPO] and [POO] are used, instead. This replacement does not affect the output voltage because the vectors [PPO] and [OON], [POO] and [ONN] generate the same output voltage. The switching sequence is [PPO]-[POO]-[PON] and return. The dwell-times of these vectors can be obtained by the same way as the conventional method [32].

In sectors II and V, medium vectors [OPN] and [ONP] cannot be reached in postfault operation. Unfortunately, these vectors do not have any redundant vectors. Therefore, the three-level operation is not ensured in sectors II and V. The FT method introduces two-level operation in sectors II and V. In detail, if the reference vector falls in sector II, three voltage vectors  $\vec{V}_0$ ,  $\vec{V}_{14}$ , and  $\vec{V}_{15}$  are utilized to synthesize the reference vector. It is worth noting that vectors [PPP] and [NNN] are used instead of zero vector [OOO]. The switching sequence for sector II is [PPP]-[PPN]-[NPN]-[NNN] and return. The dwell-time calculations for these vectors are expressed as

$$\begin{cases} t_{14} = MT_s \sin(2\pi/3 - \theta) \\ t_{15} = MT_s \sin(\theta - \pi/3) \\ t_0 = T_s - t_{14} - t_{15} \end{cases}$$

(9)

In this method, the faulty phase is working as a two-level inverter while the healthy phase is still working as a three-level inverter.

#### D. OCF at $D_1/D_4$ , SCF at $D_2/D_3$ , and SCF at $S_P/S_N$

The OC-FT methods for OCFs of  $S_P/S_N$ ,  $S_{1X}/S_{4X}$ , and  $S_{2X}/S_{3X}$  are the main contributions of this article. However, these three methods can cover some extra semiconductor failures. In OC-FT method for  $S_{1A}$ , switches  $S_{1B}$  and  $S_{1C}$  are always turned OFF. Hence, this control method can be extended to solve the OCF of  $S_{1A}$ ,  $S_{1B}$ , and  $S_{1C}$  that occurs at the same time. This cannot do in the conventional methods [26]–[31]. Moreover, diodes  $D_1$  and  $D_2$  are always reverse biased and forward biased. Thus, this control scheme can be used to handle with the OCF of  $D_1$  and the SCF of  $D_2$ . In this case, switch  $S_P$  is

Fig. 8. Flowchart of FT operation of TLB-T2I.

always gated on, thus,  $S_P$  SCF can be addressed by this control technique. Because of the symmetry of TLB-T<sup>2</sup>I, the OCF at  $D_4$ , SCF at  $D_3$  and  $S_N$ , can be solved by the same way.

#### E. OCF at $D_2/D_3$ and SCF at $D_1/D_4$

In FT method for  $S_P$ , diode  $D_2$  is always reverse biased whereas  $D_1$  is always forward biased. Thus, this PWM method can be applied to solve the OCF of  $D_2$  and the SCF of  $D_1$ . The same way can be used to handle with OCF at  $D_3$ , and SCF at  $D_4$ , because of system symmetrical characteristic.

#### F. OCF/SCF at Upper/Lower Capacitors

Like switching devices, the capacitor is also able to face with OCF or SCF. The SCF at the capacitor usually causes a high SC current through the capacitor. It results in destroying this capacitor, and the SCF is changed to an OCF. It can be seen that the FT methods for  $S_P$  and  $S_{1A}$  OCFs do not use upper capacitor  $C_P$ . Therefore, both methods can be used to solve the OCF of capacitor  $C_P$ . The same way can be applied to handle with the OCF of capacitor  $C_N$ .

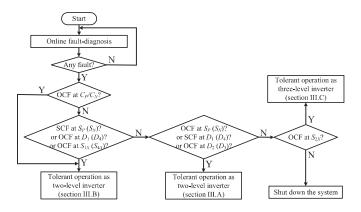

#### G. Flowchart of Fault-Tolerant Operation

The flowchart of FT operation of TLB-T<sup>2</sup>I is shown in Fig. 8. An online diagnosis is adopted to monitor the system. The fault-diagnosis method in [9] can be applied for online fault-diagnosis function. If any fault is detected, it is addressed depending on type of fault. If the fault is OCF at  $C_P/C_N$  or SCF at  $S_P/S_N$  or OCF at  $D_1/D_4$  or OCF of  $S_{1\,X}/S_{4\,X}$ , the FT method introduced in Section III.B is activated. If the fault is OCF at  $S_P/S_N$  or SCF at  $D_1/D_4$  or OCF at  $D_2/D_3$ , the FT method introduced in Section III-A is utilized. If the fault occurs at bidirectional switch  $S_{2\,X}/S_{3\,X}$ , the FT method introduced in Section III-C is activated. The system is stopped when any another type of fault is detected.

#### IV. DESIGN GUIDELINES AND POWER LOSS CONTRIBUTION

#### A. Design Guidelines

The component selection is presented to ensure the operation of the inverter in both normal and failure cases. When the

TABLE II

INVERTER COMPONENTS

| Components                    | Parameters                                                      |

|-------------------------------|-----------------------------------------------------------------|

| $S_P/S_N$ and $S_{1X}-S_{4X}$ | IMW120R020M1H (1200 V, 98 A, $r_{ds,on} = 19 \text{ m}\Omega$ ) |

| $D_1/D_4$                     | IMW120R020M1H (1200 V, 60 A, $V_F = 1.5 \text{ V}$ )            |

| $D_2/D_3$                     | VS-65EPS12LHM3 (1200 V, 65 A, $V_F = 1.12 \text{ V}$ )          |

| $L_B$                         | $3 \mathrm{mH} / 50 \mathrm{m}\Omega$                           |

| $C_P/C_N$                     | $2.2 \mathrm{mH/50 m} \Omega$                                   |

Fig. 9. Power loss analysis for the TLB-T<sup>2</sup>I.

inverter changes from normal to failure mode ( $S_P/S_{1A}$  OCFs), the component rating is obviously increased. Therefore, the inverter is designed to ensure the postfault operation of  $S_P/S_{1A}$  OCF. The voltage rating of all semiconductor devices and capacitors is maximized when applying FT methods for  $S_P/S_{1A}$  OCFs, which equals to the dc-link voltage,  $V_{PN}$ . Similarly, the current rating of all devices is maximized when applying  $S_P$  FT method, which is equal to the inductor current. Therefore, the semiconductor devices, inductor, and capacitors are selected to operate with dc-link voltage and input current. Under  $S_P/S_{1A}$  OCF, the boost circuit behaves as a conventional dc-dc boost converter. Therefore, the inductor and capacitor are selected like a conventional boost circuit as follows:

$$\begin{cases}

L_B \ge V_{\text{dc}} DT_S / (x\% I_L) \\

C_P = C_N \ge I_{PN} D(1 - D) T_S / (y\% V_{\text{dc}})

\end{cases}$$

(10)

where x% and y% are percentages of inductor current ripple and capacitor voltage ripple,  $T_S$  is the switching period.

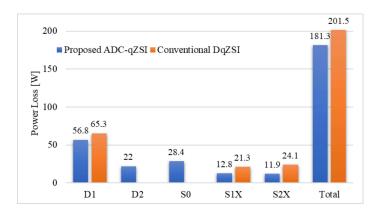

#### B. Power Loss Contribution

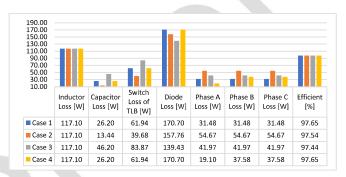

The power loss calculation for the TLB-T<sup>2</sup>I is conducted in four cases as follows: case 1) normal condition, case 2) post-fault operation of  $S_P$  OCF, case 3) postfault operation of  $S_{1A}$  OCF, and case 4) postfault operation of  $S_{2A}$  and  $S_{3A}$  OCF. The system parameters used for power loss calculation are given in Table II. The inverter is designed to operate with 400 V input voltage, 220 V<sub>RMS</sub>/380 V<sub>RMS</sub> three-phase output voltage, and 20 kVA. The dc-link voltage,  $V_{PN}$ , is boosted to 800 V. With the help of PSIM software, the power loss analysis of the inverter under the four cases mentioned above is obtained, as shown in Fig. 9. The inverter can obtain a high efficiency (97.65% for case 1) if it is carefully designed. With the help of new generation of semiconductor devices like SiC MOSFET/Diode, the performance of the inverter is not too much changed when it goes from normal

357

358

359

360

361

362

363

364

365

366

367

368

369

370

371

372

373

374

375

376

377

378

379

380

381 382

383

384

385

386

387

388

Two-stage Inverter (Fig. 1) 3L-qZSI [29] 3L-qSBI [30] 3L-qSBI [31] Proposed Method 1/(1-2D) for F11/(1-D) for F1 and F2 and Boost factor, B 1/(1-D) for F2 and F3 1/(1-2D) for F2 and F31/(1-2D) for F2 and F. 2/(1-2D) for F2 and F3  $M \times B / \sqrt{3}$  for F2 $2M \times B / \sqrt{3}$  for F1 and Voltage gain, G  $2M \times B / \sqrt{3}$  for F3  $2M \times B / \sqrt{3}$  for F3  $2M \times B / \sqrt{3}$  for F3  $2M \times B / \sqrt{3}$  for F1 and F3 F2 and F3Capacitor voltage B for F1B/2 for F3B/2 for F2 and F3(1-D)B/2 for F2 and F3B/2 for F2 and F3B/2 for F2 and F3B for F1 and F2stress,  $V_C/V_{dc}$ Diode voltage stress, B for F1 B/2 for F3B/2 for F2 and F3B/2 for F2 and F3B/2 for F2 and F3B for F1 and F2 $V_D/V_{dc}$ B/2 for F2 and F3Switch  $S_P / S_N$  voltage B for F1B/2 for F3B/2 for F2 and F3B/2 for F2 and F3NA B for F1 and F2stress,  $V_S/V_{dc}$ B/2 for F2 and F3Switch S<sub>4X</sub> voltage B for F2 and F3 B for F2 and F3 B for F2 and F3 B for F1 and F2 and F3 B for F1 and F2 and F3 stress,  $V_{S4X}/V_{dd}$ Capacitors 4 Diodes 4 F2 and F3 F2 and F3 F2 and F3F1 and F2 and F3F1 and F2 and F3Fault-tolerant Tolerate multiple OCI No No Yes at  $S_{1X}/S_{4X}$ Solving diode OCF of  $D_2/D_3$ OCF/SCF of  $D_1$ ,  $D_2$ ,  $D_3$ NA NA NA OCF/SCF SCF of  $D_1/D$  $D_4$ Solving boost switch OCF & SCF NA NA NA OCE  $(S_P/S_N)$  OCF/SCF Solving capacitor OCF NA NA NA Yes Yes

TABLE III

COMPARISON BETWEEN PROPOSED METHOD WITH OTHERS UNDER OC FAULT-TOLERANT

$F1: S_P ext{ OCF } F2: S_{1A} ext{ OCF } F3: S_{2A} ext{ and } S_{3A} ext{ OCFs NA: Not Applicable}$

operation to FT operation. For example, the efficiency of the inverter is only decreased by 0.21% when the  $S_{1A}$  FT method is activated and by 0.11% for the  $S_P$  FT method.

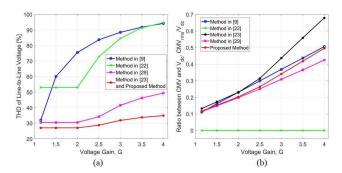

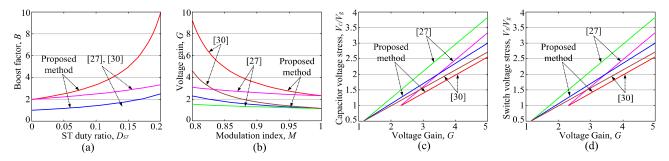

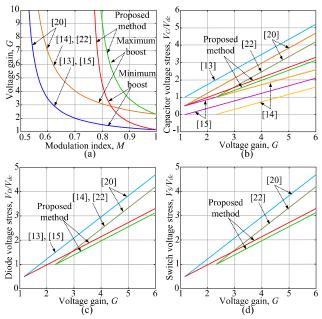

#### V. COMPARISON STUDY

In this section, the conventional control technique presented in [26] is considered to compare with the proposed method. Note that, in the FT method for half-bridge switch OCF, this method reduces the output voltage to half of that in normal condition. Therefore, in order to be fair, the conventional two-stage inverter shown in Fig. 1 is utilized to employ the method in [26]. In post faultoperation, the boost network produces more dc-link voltage to compensate for the degradation of output voltage. The other configurations, which are three-level quasi-Z-source inverter (3L-qZSI) in [29] and three-level quasi-switched boost inverter (3L-qSBI) in [30] and [31], are also considered in this comparison. In [29]–[31], the dc-link boost characteristic is ensured by the impedance-source network. The overall comparison is given in Table III. To put it simply, symbols F1, F2, and F3 are respectively used for OCFs of  $S_P$ ,  $S_{1A}$ , and bidirectional switch  $S_{2A}/S_{3A}$ .

The qZS network in [29] uses the largest number of inductors and capacitors. The works in [30] and [31], two-stage inverter, and proposed method require smaller passive components than [29]. For the OCF at  $S_{1A}$ , the bidirectional switch of the faulty phase is always turned ON during post-fault condition and two healthy phases are used to recover output voltage, in [26], [29]–[31]. Thus, the works in [29]–[31] and two-stage inverter just solve a single OCF at one upper switch of the inverter branch ( $S_{1A}$ , or  $S_{1B}$ , or  $S_{1C}$ ). While the proposed method turns OFF all upper switches when OCF occurs in one of these three switches. As a result, this scheme can be extended to solve multiple upper or lower switch OCFs, as given in Table III. Moreover, the proposed techniques can address many types of device failures of

TLB circuit, which have not been mentioned in previous studies. Full OCFs/SCFs of switch  $S_P/S_N$ , and OCFs/SCFs of diodes  $D_1 - D_4$  are not well discussed in [29]–[31], and two-stage inverter, while these failures can be solved by proposed methods. Furthermore, the OCF of capacitors  $C_P$  and  $C_N$  can be addressed by the proposed method and method in [31], which is not obtained in two-stage inverter and methods in [29] and [30]. There are two FT methods for OCF of the capacitor, whereas there is only one control technique for this failure in [31]. As a result, the proposed techniques are more flexible than the work in [31].

389

390

391

392

393

394

395

396

397

398

399

400

401

403

404

405

406

407

408

409

410

411

412

414

415

417

418

419

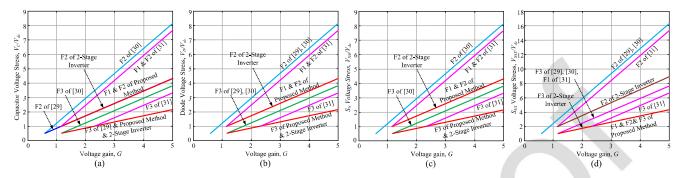

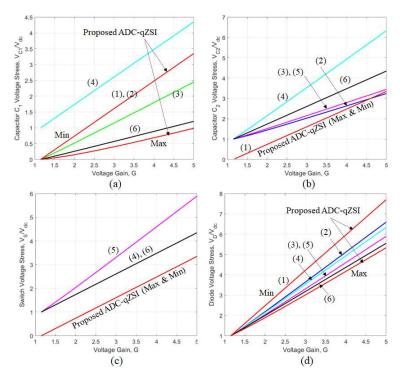

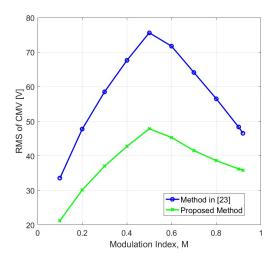

The comparison of voltage stress on devices in post-fault condition is shown in Fig. 10. To be simple, only the maximum value of voltage stress is mentioned in this comparison. For example, there are four capacitors in 3L-qZSI. However, only max value of capacitor voltages is considered in this work. Among these studies, the proposed method, conventional two-stage inverter, and method in [29] produce the smallest capacitor voltage rating for F1, F2, and F3 FT methods. This advantage can be achieved by using many capacitors in [29] and a large modulation index in the proposed scheme and a two-stage inverter.

The diode and switch voltage stresses are affected by the dclink voltage. The dc-link voltage depends on the modulation index. In detail, the dc-link voltage can be calculated as follows:

$$V_{PN} = 2 \times V_{x,\text{peak}}/M. \tag{11}$$

In (11), the use of a larger modulation index produces a smaller dc-link voltage requirement, which causes reduction of voltage stress on diodes and switches, as shown in Fig. 10(b) and (c). The TLBT<sup>2</sup>I with proposed method can operate at highest modulation index as the conventional two-stage inverter. As a result, it produces lower voltage ratings on diodes and switches than other works in [29]–[31]. Especially, in the F2 FT method, the proposed method uses only one capacitor  $C_N$  while the

Fig. 10. Comparison between proposed method and others. (a) G vs. capacitor voltage stress. (b) G versus diode voltage stress. (c) G versus boost network switch voltage stress. (d) G versus  $S_{4X}$  switch voltage stress.

Fig. 11. Experimental prototype.

conventional two-stage inverter uses both capacitors  $C_P$  and  $C_N$ . Thus, the proposed method can reduce the voltage rating of  $S_{4X}$  by 50% when compared to the conventional two-stage inverter, as shown in Fig. 10(d).

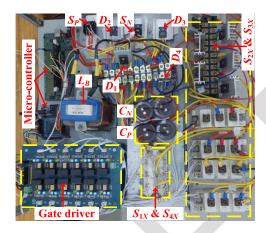

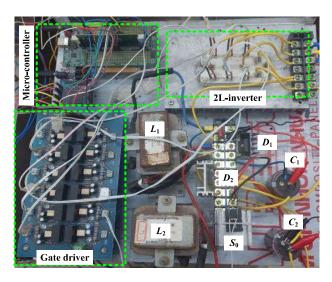

#### VI. EXPERIMENTAL RESULTS

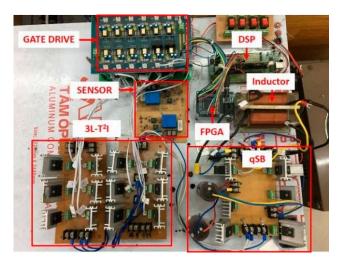

A 1-kW laboratory prototype, shown in Fig. 11, has been built to verify the accuracy of the proposed methods. The T-type inverter is based on a six IGBTs SKMGD123D module, a SKM75GB12T4 modules and diodes DSEI60-12A. The TLB network is constructed by MOSFETS 60R060P7 and diodes VS-60APF12-M3. Because of the limitations of the laboratory, the optimal prototype cannot be obtained. The inverter and control parameters used in the experiment are given in Table IV. Note that only three main FT methods for  $S_P$ ,  $S_{1A}$ , and bidirectional switch  $S_{2A}$  and  $S_{3A}$  OCFs are included in the experiment. The fault-detection method can be found in many studies like [8], [9]. In particular, the switch voltage can feedback to the microcontroller to detect semiconductor failure, quickly [9]. Therefore, this article just focuses on verifying the FT methods. Wang et al. [24], [25], the OCF is generated by cutting of the corresponding control signal. All the OCFs are assumed to appear at the beginning of phase A output voltage. The fault operation occurs during a single output period. The corresponding FT method is activated in the next output period.

### TABLE IV EXPERIMENTAL PARAMETERS

| Parameter/ Comp        | onents              | Values                       |

|------------------------|---------------------|------------------------------|

| DC input source        | $V_{dc}$            | 200 V                        |

| AC output voltage      | $V_{x,RMS}$         | $110 \text{ V}_{\text{RMS}}$ |

| Line frequency         | $f_0$               | 50 Hz                        |

| Switching frequency    | $f_s$               | 10 kHz                       |

| Boost inductor         | $L_B$               | 3 mH/20 A                    |

| Boost Capacitors       | $C_P$ and $C_N$     | 1 mF/800 V                   |

| Low-pass filter        | $L_f \& C_f$        | 3 mH and 10 μF               |

| Resistor load          | $R_X$               | $40\Omega$                   |

| Boost switches         | $S_P$ , $S_N$       | 60R060P7                     |

| Boost diodes           | $D_1 - D_4$         | VS-60APF12-M3                |

| Upper/Lower switches   | $S_{1X}$ , $S_{4X}$ | SKMGD123D                    |

| Bidirectional switches | $S_{2X}$ , $S_{3X}$ | SKM75GB12T4 and DSEI60-12A   |

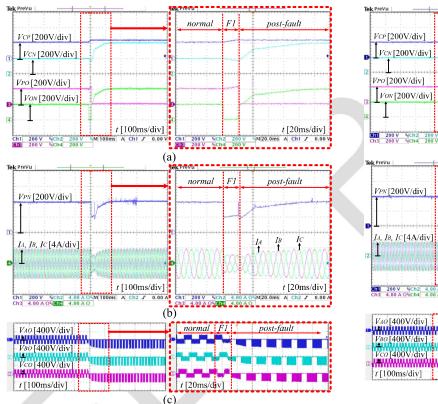

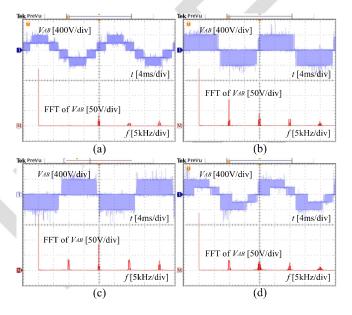

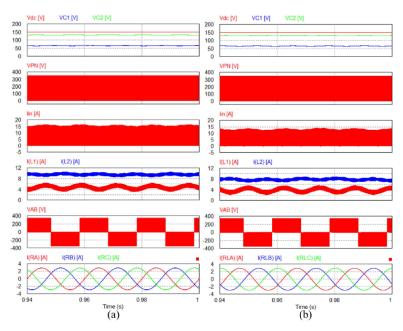

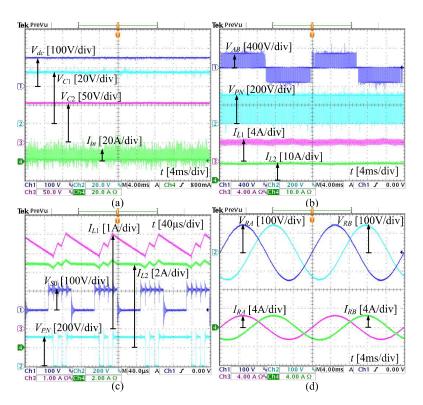

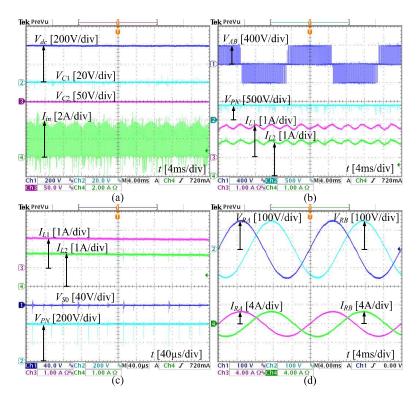

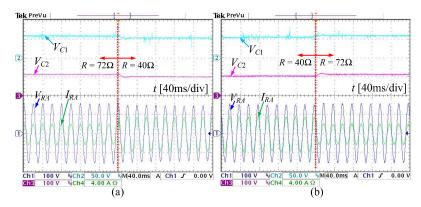

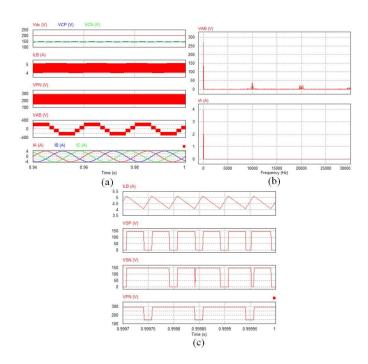

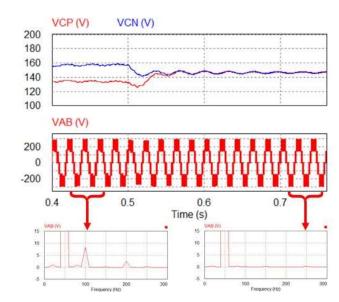

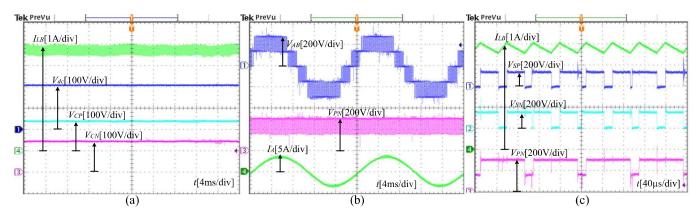

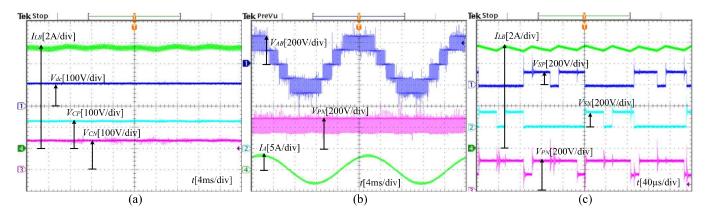

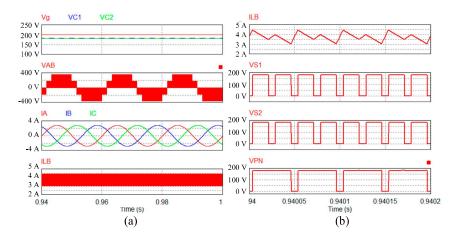

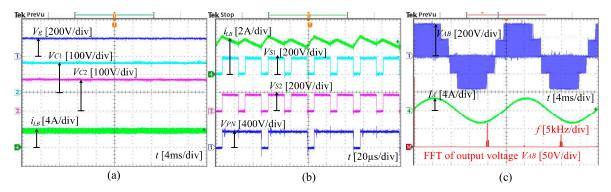

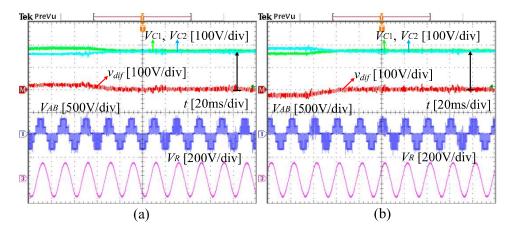

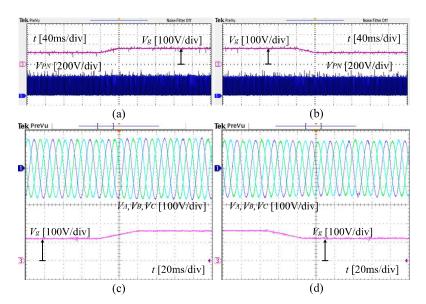

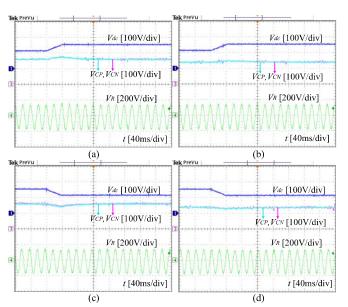

The proposed methods have been tested at 200 V input voltage. In normal condition, the two capacitor voltages are boosted to 200 V, as shown in Figs. 12 –14 and Table V. Both capacitor voltages are balanced. Thus, the dc-link voltage  $V_{PN}$  achieves 400 V. The RMS value of output current is 2.66  $A_{\rm RMS}$ . The output current waveform is sinusoidal with the help of LC filter. The output pole voltage  $V_{XO}$  has three voltage levels: +200, 0, and -200 V. The FFT spectra of output line-to-line voltage is shown in Fig. 15. The THD of output line-to-line voltage  $V_{AB}$  is 49.4%, as given in Table V.

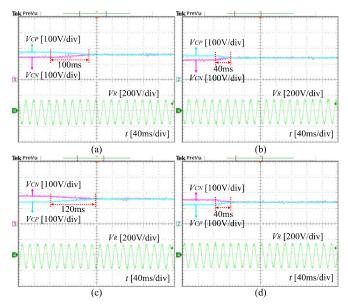

#### A. Results When S<sub>P</sub> OCF

The experimental results when OCF occurs at  $S_P$  are presented in Fig. 12. During OCF of  $S_P$ , the drain-source of  $S_P$  is opened, whereas the lower switch  $S_N$  operates normally. It makes capacitor  $C_P$  voltage slightly increase, whereas lower capacitor  $C_N$  voltage is slightly decreased, as shown in Fig. 12(a). The output pole voltage and output load current have critical distortion, as illustrated in Fig. 12(b) and (c).

Under the proposed method, the UST of inverter side is activated, which causes capacitor  $C_P$  to be disconnected from the main circuit. Thus, the capacitor voltage  $V_{CP}$  keeps constant during post-fault condition, as shown in Fig. 12(a). In this time interval, the dc-link voltage is equal to  $C_N$  voltage. With 400 V of  $C_N$  voltage, the dc-link voltage is maintained as that in normal condition, which helps to recover the amplitude of output load current, as presented in Fig. 12(b). The output pole voltage  $V_{XO}$  has two voltage levels, which are 0 and -400 V, in

Voltage rating, RMS current  $THD_{VAB}$  $S_{4B}$  $S_P$  $S_N$  $D_1$  $D_2$  $D_3$  $S_{4A}$ 200 V 200 V 200 V 0 V 0 V 200 V 400 V 400 V 400 V 200 V 400 N 200 V 200 V Normal 200 V 49.4% 1.86<u>A</u> 1.86<u>A</u> 3.58 A 3.58 A 3.58 A 3.17 A 3.17 A 3.58 A 1.75 A 1.75 A 1.75 A 1.75 A 400 V 400 V 0 V 200 V 400 V 400 V 400 V 400 V 400 V 400 N 400 V 200 V 400 V 96.3% 3.58 A 5.43 A 0 A 3.43 A 3.81 A 4.21 A 197 A 1.82. A 421 A 1.97 A 1.82. A  $0 \, \overline{V}$ 0 V400 V 0 V 0 V 400 V 99.8% F2 0 V Fault 5.56 A 3.58 A 5.56 A 3.94 A 2.27 A 0 A 3.64 A 2.27 A 200 V 200 V 200 V 0 V 0 V 200 V 400 V 400 V 400 V 200 V 400 V 200 V F3 200 V 66.7% 1.74 A 1.81 A 3.58 A 3.58 A 3.58 A 3.17 A 3.17 A 3.58 A 1.81 A

TABLE V

EXPERIMENTAL COMPARISON BETWEEN NORMAL AND FAULT CONDITIONS

normal

Fig. 12. Experimental results for  $S_P$  OC FT method.

Fig. 13. Experimental results for  $S_{1A}$  OC FT method.

post-fault operation. Because the proposed method does not use the voltage vector [NNN], the output pole voltages are clamped to the dc-link mid-point in one-third of the output voltage period, as illustrated in Fig. 12(c). The FFT spectra of  $V_{AB}$  in postfault operation of  $S_P$  OCF is shown in Fig. 15(b). The THD of output line-to-line voltage  $V_{AB}$  is 96.3%, which is higher than that in normal condition because the inverter now operates with a two-level output voltage.

#### B. Results When $S_{1A}$ OCF

472

473

474

475

476

477

478

479

480

481

482

483

484

485

486

Fig. 13 shows the experimental results for the  $S_{1A}$  OCF FT method. When OCF of switch  $S_{1A}$  occurs, the output voltage  $V_{AO}$  cannot achieve a value of +200 V, as shown in Fig. 13(c). It results in the distortion of phase A load current in the positive half cycle, as illustrated in Fig. 13(b). The distortion of phase A current also affects two healthy phase currents.

When activating the proposed method, the capacitor  $C_P$  voltage is discharged from 200 V to zero with the help of healthy upper switches,  $S_{1B}$  and  $S_{1C}$ . The capacitor  $C_N$  voltage is boosted to 400 V, as shown in Fig. 13(a). In steady-state, the dc-link voltage,  $V_{PN}$ , is equal to  $V_{ON}$ , because the upper capacitor voltage is zero. The dc-link voltage and output load currents are equal to that in normal condition. The FFT spectra of  $V_{AB}$  is shown in Fig. 15(c). The THD output line-to-line voltage is 99.8%, as presented in Table V.

488

489

490

491

492

493

494

495

496

497

498

499

500

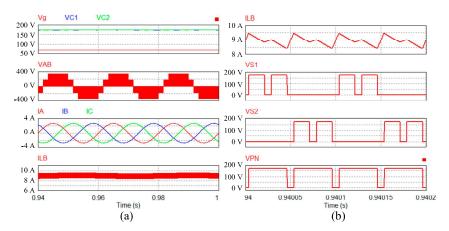

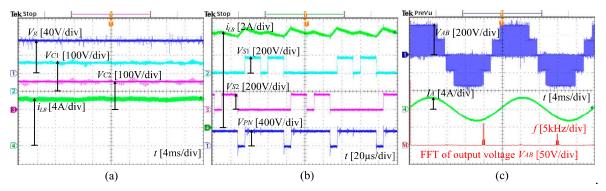

#### C. Results When $S_{2A}$ and $S_{3A}$ OCFs

The experimental results for bidirectional switch OCF are presented in Fig. 14. Compared to the OCFs of  $S_P$  and  $S_{1A}$ , the OCFs of  $S_{2A}$  and  $S_{3A}$  generate less serious distortion in output currents. The proposed method, based on a modified SVM method, is applied to address this problem. As mentioned

Fig. 14. Experimental results for bidirectional switch OC FT method.

Fig. 15. FFT spectra of output line-to-line voltage under (a) normal condition and FT methods for (b)  $S_P$  OCF, (c)  $S_{1A}$  OCF, and (d)  $S_{2A}$  and  $S_{3A}$  OCFs.

in Section III-C, phase A is introduced to generate two-level output voltage, whereas the other healthy phases operate with three-voltage levels at output terminals, as shown in Fig. 14(c). At most times of the output period, phase A is clamped to positive/negative point of dc-link voltage. The amplitudes of dc-link

Fig. 16. Experimental efficiency.

voltage and output load current are equal to those in normal condition. This method causes a slight oscillation in capacitor voltages. However, these capacitor voltages are still balanced and do not have a critical effect to output current quality. The FFT spectra of  $V_{AB}$  is presented in Fig. 15(d). As given in Table V, the F3 FT method produces a smaller THD value at  $V_{AB}$  than the F1 and F2 FT methods, which is 66.7%. Except for F2, both FT methods for  $S_P$  and  $S_{1A}$  cause voltage and current rating increment.

#### D. Inverter Efficiency

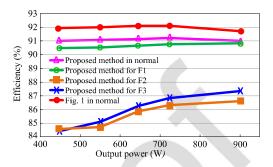

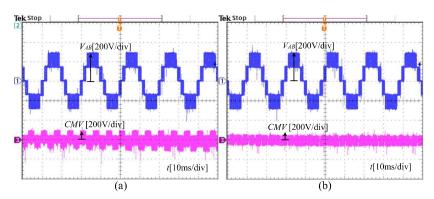

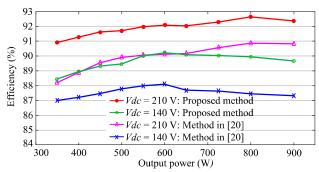

The system efficiency under normal and failure modes of the proposed methods are presented in Fig. 16. The measured efficiency of the conventional topology in Fig. 1 in normal condition is also considered in this experiment. By adding two diodes  $(D_2 \text{ and } D_3)$  to achieve FT capability, the efficiency of TLBT<sup>2</sup>I is slightly lower (just 0.91% at 725-W) than the topology in Fig. 1. In FT methods for  $S_P$  fault (F1) and  $S_{1A}$  fault (F2), the switch voltage stress is increased, which leads to increase both switching and conduction losses. For example, the duty ratio of switch  $S_P$  will be increased when the inverter changes from normal to F1 mode, which generates more conduction loss of switch  $S_P$ . Moreover, the use of the UST insertion method for F2 FT is also the reason for the conduction loss increment. As a result, the system efficiencies in these cases are lower than in normal and bidirectional switch fault conditions.

#### VII. CONCLUSION

The full OCF of semiconductor devices as well as SCF at diodes/switches of TLB-T<sup>2</sup>I was addressed with the introduced PWM methods. The voltage rating of devices like capacitors and semiconductors was improved compared to existing PWM methods, significantly. This benefit has been demonstrated through some comparison studies. Under the proposed method for upper or lower switch OCF, the voltage rating of inverter half-bridge switches was reduced at least to half of that in conventional methods. Moreover, the proposed methods can cover all diode and boost switch OCFs and SCFs. The failure of the capacitor was also addressed with the proposed methods. Thus, it was concluded that the system reliability was improved. The experiment was conducted to validate the accuracy of the introduced theory.

623

624

625

626

627

628

629

630

631

632

633

634

635

636

637

638

639

640

641

642

643

644

645

646

647

648

649

650

651

652

653

654

655

656

657

658

659

660

661

662

663

664

665

666

667

668

669

670

671

672

673

674

675

676

677

678

680

681

682

683

684

685

547 548 549

> > 562

554

569

570

578

579

587

588

> > 608

609 610

598

599

600

611 612

613 614 617

621

REFERENCES

- [1] M. Hassanifar, D. Nazarpour, S. Golshannavaz, and Y. Neyshabouri, "A modular cascaded multilevel converter with high configurability: Design, analysis, and optimization study," IEEE J. Emerg. Sel. Topics Power Electron., to be published, doi: 10.1109/JESTPE.2021.3114501.

- [2] S. Xu, J. Zhang, and J. Hang, "Investigation of a fault-tolerant threelevel T-type inverter system," IEEE Trans. Ind. Appl., vol. 53, no. 5, pp. 4613-4623, Sep./Oct. 2017.

- [3] U. Choi, J. Lee, F. Blaabjerg, and K. Lee, "Open-circuit fault diagnosis and fault-tolerant control for a grid-connected NPC inverter," IEEE Trans. Power Electron., vol. 31, no. 10, pp. 7234-7247, Oct. 2016.

- H. K. Jahan, F. Panahandeh, M. Abapour, and S. Tohidi, "Reconfigurable multilevel inverter with fault-tolerant ability," IEEE Trans. Power Electron., vol. 33, no. 9, pp. 7880-7893, Sep. 2018.

- V. T. Tran, M. K. Nguyen, D. T. Do, and D. Vinnikov, "An SVM scheme for three-level quasi-switched boost T-type inverter with enhanced voltage gain and capacitor voltage balance," IEEE Trans. Power Electron., vol. 36, no. 10, pp. 11499-11508, Oct. 2021.

- A. T and N. R. Patne, "Fault tolerant control of Z-source neutral point clamped inverter," in Proc. 15th IEEE India Council Int. Conf., 2018.

- [7] D. Do and M. Nguyen, "Three-level quasi-switched boost T-type inverter: Analysis, PWM control, and verification," IEEE Trans. Ind. Electron. vol. 65, no. 10, pp. 8320-8329, Oct. 2018.

- M. di Benedetto, A. Lidozzi, L. Solero, F. Crescimbini, and P. J. Grbović, 'Reliability and real-time failure protection of the three-phase five-level E-type converter," IEEE Trans. Ind. Appl., vol. 56, no. 6, pp. 6630-6641, Nov/Dec. 2020.

- M. Yaghoubi, J. S. Moghani, N. Noroozi, and M. R. Zolghadri, "IGBT open-circuit fault diagnosis in a quasi-Z-source inverter," IEEE Trans. Ind. Electron., vol. 66, no. 4, pp. 2847-2856, Apr. 2019.

- [10] U. Choi, K. Lee, and F. Blaabjerg, "Diagnosis and tolerant strategy of an open-switch fault for T-type three-level inverter systems," IEEE Trans. Ind. Appl., vol. 50, no. 1, pp. 495-508, Jan./Feb. 2014.

- Y. Liang, R. Wang, and B. Hu, "Single-Switch open-circuit diagnosis method based on average voltage vector for three-level T-Type inverter,' IEEE Trans. Power Electron., vol. 36, no. 1, pp. 911–921, Jan. 2021.

- P. G. Ipoum-Ngome, R. C. C. Flesch, D. L. Mon-Nzongo, J. Tang, T. Jin, and M. Wang, "Fault-Tolerant model-free predictive controller for multilevel cascaded H-bridge inverters with faulty cells," IEEE Trans. Ind. Electron., vol. 69, no. 12, pp. 12225-12236, Dec. 2022.

- [13] R. Choupan, S. Golshannavaz, D. Nazarpour, and M. Barmala, "A new structure for multilevel inverters with fault-tolerant capability against open circuit faults," Electric Power Syst. Res., vol. 168, pp. 105-116, Mar. 2019.

- [14] D. Kumar, R. K. Nema, and S. Gupta, "Development of a novel faulttolerant reduced device count T-type multilevel inverter topology," Int. J. Elect. Power Energy Syst., vol. 132, May 2021, Art. no. 107185.

- [15] B. Long, T. Cao, D. Shen, J. Rodriguez, J. M. Guerrero, and K. T. Chong, 'Sequential model predictive fault-tolerance control for T-type three-level grid-connected converters with LCL filter," IEEE Trans. Ind. Electron., vol. 69, no. 9, pp. 9039–9051, Sep. 2022.

- [16] J. Chen, C. Zhang, A. Chen, and X. Xing, "Fault-tolerant control strategies for T-type three-level inverters considering neutral-point voltage oscillations," IEEE Trans. Ind. Electron., vol. 66, no. 4, pp. 2837–2846, Apr. 2019.

- [17] U. Choi, F. Blaabjerg, and K. Lee, "Reliability improvement of a T-type three-level inverter with fault-tolerant control strategy," IEEE Trans. Power Electron., vol. 30, no. 5, pp. 2660-2673, May 2015.

- W. Zhang and D. Xu, "Fault analysis and fault-tolerant design for parallel redundant inverter systems in case of IGBT short-circuit failures," IEEE J. Emerg. Sel. Topics Power Electron., vol. 6, no. 4, pp. 2031-2041, Dec. 2018

- [19] Z. Wang, J. Chen, M. Cheng, and Y. Zheng, "Fault-tolerant control of paralleled-voltage-source-inverter-fed PMSM drives," IEEE Trans. Ind. Electron., vol. 62, no. 8, pp. 4749-4760, Aug. 2015.

- [20] F. Gao, P. C. Loh, F. Blaabjerg, and D. M. Vilathgamuwa, "Performance evaluation of three-level Z-source inverters under semiconductorfailure conditions," IEEE Trans. Ind. Appl., vol. 45, no. 3, pp. 971-981,

- [21] X. Wang et al., "Fault-Tolerant control of common electrical faults in dual three-phase PMSM drives fed by T-Type three-level inverters," IEEE Trans. Ind. Appl., vol. 57, no. 1, pp. 481–491, Jan./Feb. 2021.

- [22] J. He, R. Katebi, N. Weise, N. A. O. Demerdash, and L. Wei, "A fault-tolerant T-type multilevel inverter topology with increased overload capability and soft-switching characteristics," IEEE Trans. Ind. Appl., vol. 53, no. 3, pp. 2826-2839, May/Jun. 2017.

- [23] R. Katebi, J. He, and N. Weise, "Investigation of fault-tolerant capabilities in an advanced three-level active T-type converter," IEEE J. Emerg. Sel. Topics Power Electron., vol. 7, no. 1, pp. 446-457, Mar. 2019.

- B. Wang, Z. Li, M. Dong, Z. Bai, P. T. Krein, and H. Ma, "Recovering partial three-level operation in a T-type inverter with fault management redundant unit," IEEE Trans. Power Electron., vol. 35, no. 9, pp. 8944-8955,

- [25] B. Wang, Z. Li, Z. Bai, P. T. Krein, and H. Ma, "A redundant unit to form T-type three-level inverters tolerant of IGBT open-circuit faults in multiple legs," IEEE Trans. Power Electron., vol. 35, no. 1, pp. 924–939, Jan. 2020.

- T. Lee, B. Li, M. Yang, and Y. Tsai, "A carrier-based PWM for three-level T-type inverter to tolerate open-circuit fault," IEEE Trans. Power Electron., vol. 33, no. 10, pp. 8787-8796, Oct. 2018.

- J. Li, A. Q. Huang, Z. Liang, and S. Bhattacharya, "Analysis and design of active NPC (ANPC) inverters for fault-tolerant operation of highpower electrical drives," IEEE Trans. Power Electron., vol. 27, no. 2, pp. 519-533, Feb. 2012

- [28] P. Azer, S. Ouni, and M. Narimani, "A novel fault-tolerant technique for active-neutral-point-clamped inverter using carrier-based PWM," IEEE Trans. Ind. Electron., vol. 67, no. 3, pp. 1792–1803, Mar. 2020.

- V. F. Pires, A. Cordeiro, D. Foito, and J. F. Martins, "Quasi-Z-source inverter with a T-type converter in normal and failure mode," IEEE Trans. Power Electron., vol. 31, no. 11, pp. 7462-7470, Nov. 2016.

- M. Sahoo and Si. Keerthipati, "Fault-tolerant three-level boost inverter with reduced source and LC count," *IET Power Electron.*, vol. 11, pp. 399-405, Feb. 2018.

- D. T. Do, M. K. Nguyen, T. H. Quach, V. T. Tran, F. Blaabjerg, and D. M. Vilathgamuwa, "A PWM scheme for a fault-tolerant three-level quasi-switched boost T-type inverter," IEEE J. Emerg. Sel. Topics Power Electron., vol. 8, no. 3, pp. 3029–3040, Sep. 2020.

- G. Yang, D. H. Yi, C. Chai, B. Huang, Y. Zhang, and Z. Chen, "Predictive current control of boost three-level and T-type inverters cascaded in wind power generation systems," Algorithms, vol. 11, no. 7, Jun. 2018, Art. no. 92.

- J. Kwon, B. Kwon, and K. Nam, "Three-phase photovoltaic system with three-level boosting MPPT control," IEEE Trans. Power Electron., vol. 23, no. 5, pp. 2319-2327, Sep. 2008.

- [34] H. Hu, W. Yao, and Z. Lu, "Design and implementation of three-level space vector PWM IP core for FPGAs," IEEE Trans. Power Electron., vol. 22, no. 6, pp. 2234-2244, Nov. 2007.

Duc-Tri Do was born in Vietnam in 1973. He received the B.S., M.S. and Ph.D. degrees in electronic engineering from the Ho Chi Minh City University of Technology and Education, Ho Chi Minh City, Vietnam, in 1999, 2012 and 2021, respectively.

He is currently a Lecturer with the Faculty of Electrical and Electronics Engineering, Ho Chi Minh City University of Technology and Education. His current research interests include power converters for renewable energy systems.

Vinh-Thanh Tran received the B.S. and the M.S degrees in electronic engineering in 2018 and 2020, respectively from Ho Chi Minh City University of Technology and Education, Ho Chi Minh City, Vietnam, where he is currently working toward the Ph.D. degree in electronic engineering.

current research interests include His impedance source inverter and control of multilevel inverter.

Minh-Khai Nguyen (Senior Member, IEEE) received the B.S. degree in electrical engineering from the Ho Chi Minh City University of Technology, Ho Chi Minh City, Vietnam, and the M.S. and Ph.D. degrees in electrical engineering from Chonnam National University, Gwangju, South Korea.

His current research interests include power electronics converters for electric vehicles and renewable energy systems.

Sanjeev M. Naik (Senior Member, IEEE) received the Bachelor's degree from IIT Bombay, Bombay, India, in 1986, the M.S.E.E. degree from the University of Michigan, Ann Arbor, MI, USA, in 1988, and the Ph.D. degree from the University of Illinois, Urbana-Champaign, Champaign, IL, USA, in 1992, all in electrical engineering, and the M.B.A. degree from the University of Michigan in 2000.

He leads the Advanced Systems Develop-

ment team responsible for Électric Drives &

Electrification Electronics in GM's Global Electrification and Battery Systems organization. He has held multiple management and technical leadership positions in vehicle electrification, propulsion controls, x-by-wire systems, semiautonomous vehicles, and controls at GM and Cummins. Sanjeev is a recipient of GM's Boss Kettering Award, the Charles McCuen R&D Award, and the Chairman's Honors Award. He has several publications and over fifty patents. His technical interests are in developing innovative electric mobility solutions.

Dr. Naik is a Member of SAE International.

710 711

712

713

715

716 717

697

698

700

701

702

Article

# An DPWM for Active DC-Link Type Quasi-Z-Source Inverter to Reduce Component Voltage Rating

Duc-Tri Do D, Vinh-Thanh Tran and Khai Nguyen \*D

Faculty of Electrical and Electronics Engineering, Ho Chi Minh City University of Technology and Education, Ho Chi Minh City 700000, Vietnam; tridd@hcmute.edu.vn (D.-T.D.); thanhtv.ncs@hcmute.edu.vn (V.-T.T.)

\* Correspondence: khainm@hcmute.edu.vn; Tel.: +84-28-3722-1223

Abstract: The conventional DC-link type quasi-Z-source inverter has been known as a buck-boost inverter with a low component voltage rating. This paper proposes an active DC-link type quasi-Z-source inverter by adding one active switch and one diode to the impedance-source network to enhance the voltage gain of the inverter. As a result, the component voltage rating of the inverter is significantly reduced, which is demonstrated through some comparisons between the proposed topology and others. A discontinuous pulse width modulation (DPWM) scheme is proposed to control the inverter, which reduces the number of commutations compared to the traditional strategy. Under this approach, the insertion of a shoot-through state does not cause any extra commutations compared to the conventional voltage-source inverter. Details about control implementation, steady-state analysis, and design guidelines are also presented in this paper. Simulation and a laboratory prototype have been built to test the proposed inverter. Both buck and boost operations of the proposed inverter are implemented to validate the performance of the inverter.

**Keywords:** active quasi-Z-source inverter; DC-link type; discontinuous pulse width modulation; switching commutation reduction; impedance-source inverter

Citation: Do, D.-T.; Tran, V.-T.; Nguyen, K. An DPWM for Active DC-Link Type Quasi-Z-Source Inverter to Reduce Component Voltage Rating. *Energies* **2022**, *15*, 4889. https://doi.org/10.3390/ en15134889

Academic Editor: Waqar Uddin

Received: 5 June 2022 Accepted: 1 July 2022 Published: 4 July 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

Presently, inverters that convert energy from a DC input source to AC output voltage play an important role in the renewable energy system. Because of their simple structure, low component utilization, and high power density, conventional two-level inverters are used in a wide range of industrial applications [1-4]. Two forms of traditional twolevel inverters are voltage source inverters (VSI) and current source inverters (CSI). The VSI works as a voltage buck converter, where the peak-to-peak value of the AC output phase voltage is smaller than the DC link voltage. In comparison with VSI, the CSI is known as a boost converter, which uses many extra elements such as diodes [3]. Nowadays, inverters adopting a wide range of input voltage have attracted many researchers. However, conventional VSI and CSI do not adopt a wide range of input sources. In fact, the traditional solution installs a DC-DC boost converter in front of the conventional VSI to provide buckboost characteristics in two-stage power conversion. In this way, the input voltage is enhanced before feeding to the inverter circuit. In this solution, a short-circuit current generated by activating all switches in one or more phase legs can destroy the system. This state is known as the shoot-through (ST) state and is forbidden in VSI. To avoid this dangerous situation, dead-time control is adopted to generate control signals for inverter switches [5,6]. In this case, the rising edge of the control signal is delayed to avoid the ST state. It causes distortion at output voltage and an increment in total harmonic distortion (THD) of output current. Many pulse-width modulation (PWM) methods based on the direction of output current have been explored to compensate for the negative effects of dead time [5,6]. However, these studies introduced more control complexity and required many additional current sensors.

Energies 2022, 15, 4889 2 of 18

In the last two decades, impedance source inverters (ISIs) (known as single-stage inverters) have been considered to solve the problems of buck-boost operation and the ST immunity of conventional VSI. The Z-source inverter (ZSI) is the first generation of ISIs, which was explored by Professor Peng in 2003 [7]. In ZSI, two capacitor voltages of the ZS network are subtracted by input voltage to produce the DC link voltage of the inverter side. Thus, it can be concluded that the capacitors are badly utilized. The quasi-Zsource inverter (qZSI) introduced a new connection type of impedance source network to overcome the limit of ZSI [8,9]. Two main types of qZSI are continuous qZSIs (CqZSI) and DC-link type/discontinuous qZSI (DqZSI). These two topologies have the same boost factor. However, the DqZSI topology has a smaller voltage rating of a capacitor than CqZSI, as presented in [8]. The main advantage of the CqZSI compared to DqZSI is that this topology has a continuous input current [8]. Many comparisons between ISIs and traditional twostage inverters have demonstrated that single-stage inverters have better system reliability and output quality [10-12]. Moreover, when the voltage gain of the inverter is less than two, the ZSI and qZSI have higher efficiency than the conventional two-stage inverter [10,12]. The work in [13] introduced a combination of a qZS network and a single-phase neutral point clamped inverter for photovoltaic (PV) applications. With generic semiconductor devices, this work can obtain 97% conversion efficiency, just like any two-stage inverter. It demonstrated that the single-stage inverter is one of the promising topologies.

Two main issues of the impedance source inverter can be listed as (1) improving boost factor and voltage gain, and (2) reducing the number of switching commutations. When the boost factor/voltage gain is improved, the required ST duty ratio is also reduced. It results in reducing conduction loss and increasing system efficiency [14]. Moreover, the ST duty ratio also affects the inductor's current profile. Thus, a lower ST duty ratio causes a smaller inductor current ripple, which reduces the size of the inductor and increases the power density of the inverter. The switching commutation increment is mainly due to ST insertion. At least two extra commutations are generated for ST insertion in conventional methods for ISIs. It leads to increased switching losses of the semiconductor devices. Many studies have discussed switching commutation and ST duty ratio reductions, as follows.

The switching commutations can be minimized by correspondingly placing ST state, which is reported in [15–17]. Accordingly, the number of switching commutations is reduced to equal that of conventional VSI in [15–17]. Many studies have reported on voltage gain improvement methods for qZSI [18-22]. The first solution to increasing voltage gain is to add more extra passive components like inductors and diodes into the impedance-source network [18,19]. The other one is using active switches in the intermediate network [20–22]. In [18,19], one or more switched inductor (SL) units, which consist of two inductors and three diodes, are used to replace single inductors in the conventional topology of ZSI/qZSI to increase voltage gain. This solution increases the cost and size of the inverter because it utilizes many inductors. In comparison to the first solution in [18,19], the second one in [20–22] can save many inductors and diodes by using one extra active switch. It is worth noting that the boost factor and voltage gain of the topologies in [20–22] are very flexible to be controlled and higher than that in [18,19]. The work in [21] presented a combination of both solutions, which adopts both SL unit and active switch in the intermediate network. Although the voltage gain of these works has increased significantly, it remains low. Moreover, the boost factor is controlled by only the ST duty ratio, which makes the inverter inflexible.

This paper presents a new topology of active DC link type qZSI (ADC-qZSI) by adding one active switch and one diode into the conventional DqZSI. With the help of these extra devices, the proposed topology introduces one extra mode besides two conventional operating modes for ISIs (ST mode and non-ST mode). In this mode, the current of the inductor is kept constant and the voltage gain is increased. It results in component voltage rating reduction. A discontinuous PWM (DPWM) control method is proposed to control this topology. In this control technique, the ST state is inserted into the phase operating with the highest reference signals. It leads to reducing the number of switching commutations

Energies 2022, 15, 4889 3 of 18

down to equal to conventional two-level VSI. The next parts of this paper include seven sections. The inverter structure and steady-state analysis and design guidelines of the proposed inverter are presented in Sections 2 and 3, respectively. Section 4 presents the semiconductor loss calculation. The comparison study, simulation and experimental results are attached in Sections 5–7.

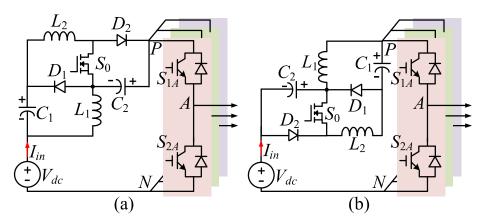

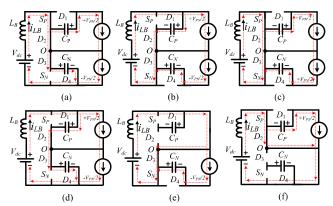

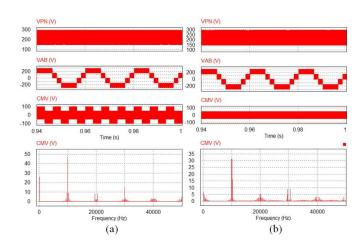

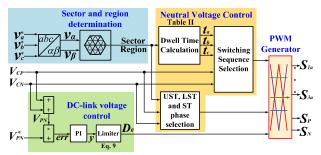

#### 2. Proposed Active DC-Link Type Quasi-Z-Source Inverter (ADC-qZSI) Topology

Two types of proposed ADC-qZSIs have been drawn in Figure 1. Both types are constructed by an ADC-qZS network followed by a conventional two-level inverter. The impedance source network is known as the boost unit and is formed by two inductors ( $L_1$  and  $L_2$ ), two capacitors ( $C_1$  and  $C_2$ ), one active switch ( $S_0$ ), and two diodes ( $D_1$  and  $D_2$ ). Compared to traditional DC-link qZSI in [8], the proposed inverter has one extra active switch,  $S_0$ , and one extra diode,  $D_2$ . This insertion makes this topology flexible to control and increases the boost factor and voltage gain of the inverter. The conventional two-level inverter is responsible for buck operation. With the corresponding control method, the proposed inverter can buck and boost the output voltage from a single DC source,  $V_{dc}$ . Each leg of the inverter side consists of two active switches,  $S_{1X}$  and  $S_{2X}$ , which ensures a two-level voltage at the output terminals,  $+V_{PN}$  and zero. In general, two types of ADC-qZSIs have similar operations, thus, type 1 shown in Figure 1a is selected for analysis.

Figure 1. Topologies of ADC-qZSI: (a) Type 1 and (b) Type 2.

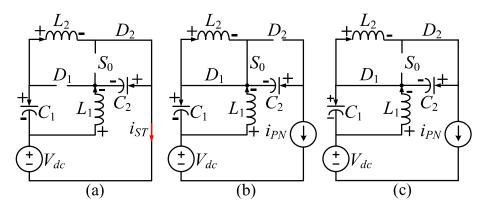

#### 2.1. Operating States

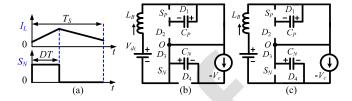

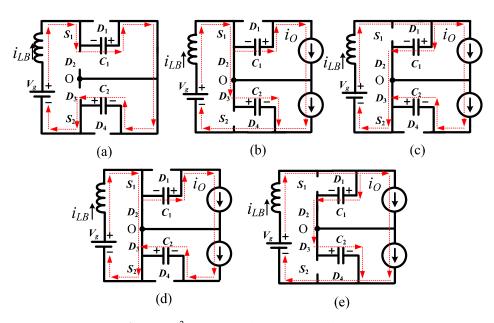

Like any single-stage inverter, the ADC-qZSI is also proposed to operate under ST mode and non-ST mode, as shown in Figure 2. The on/off states of inverter switches and diodes are listed in Table 1.

Figure 2. Operating modes of ADC-qZSI. (a) ST mode, (b) non-ST mode 1, (c) non-ST mode 2.

Energies 2022, 15, 4889 4 of 18

| Mode     | ON Switch            | ON Diode   | $V_{XN}$      |

|----------|----------------------|------------|---------------|

| ST       | $S_{1X}, S_{2X}$     | $D_2$      | 0             |

| non-ST 1 | $S_0, S_{1X}/S_{2X}$ | $D_1$      | $+V_{PN}$ , 0 |

| non-ST 2 | $S_{1X}/S_{2X}$      | $D_1, D_2$ | $+V_{PN}$ , 0 |

**Table 1.** On/Off states of ADC-qZSI (X = A, B, C).

In the ST state, as shown in Figure 2a, the inverter side is able to produce value of 0 V at three-phase output voltages by turning on two switches in one phase leg, while switch  $S_0$  is gated off. As a result, the DC-link voltage,  $V_{PN}$ , is shorted and has a value of zero. This ST state reverses diode  $D_1$  and forward diode  $D_2$  of impedance source circuit. In this mode, inductor  $L_1$  is stored energy from DC input voltage and capacitor  $C_2$ , while inductor  $C_2$  is stored energy from DC input voltage and capacitor voltages and capacitor currents are expressed as follows:

$$\begin{cases}

L_1 \frac{di_{L1}}{dt} = V_{dc} + V_{C2}; & L_2 \frac{di_{L2}}{dt} = V_{dc} + V_{C1} \\

C_1 \frac{dv_{C1}}{dt} = -i_{L2}; & C_2 \frac{dv_{C2}}{dt} = -i_{L1}

\end{cases}$$

(1)

where  $V_{dc}$  is DC input source;  $V_{C1}$  and  $V_{C2}$  are capacitor  $C_1$  and  $C_2$  voltages;  $i_{L1}$ ,  $i_{L2}$ , and  $i_{PN}$  are instantaneous values of inductor currents and equivalent inverter side current.

In non-ST mode, the DC-link voltage obtains maximum value, which is determined by the summing DC input source and two capacitor voltages. With one extra switch,  $S_0$ , the non-ST mode consists of two sub-modes depending on the state of  $S_0$ . When  $S_0$  is gated on, non-ST mode 1 shown in Figure 2b is achieved. Diode  $D_2$  is reversed bias, whereas diode  $D_1$  is forward bias. It results in shorting inductor  $L_2$  and discharging capacitor  $C_2$ . While capacitor  $C_1$  is charged from inductor  $L_1$ . The following equations are obtained:

$$\begin{cases}

L_1 \frac{di_{L1}}{dt} = -V_{C1}; L_2 \frac{di_{L2}}{dt} = 0 \\

C_1 \frac{dv_{C1}}{dt} = i_{L1} - i_{PN}; C_2 \frac{dv_{C2}}{dt} = -i_{PN}

\end{cases}$$

(2)

It can be seen that this non-ST mode maintains the energy of inductor  $L_2$  instead of discharging like conventional ISI, which increases the boost factor of the inverter.

Non-ST mode 2 of the proposed inverter, as shown in Figure 2c, is like any single-stage inverter. Switch  $S_0$  is gated off, whereas the inverter side switches operate like conventional inverters. Two inductors transfer energy to capacitors. The following equations are achieved:

$$\begin{cases}

L_1 \frac{di_{L1}}{dt} = -V_{C1}; & L_2 \frac{di_{L2}}{dt} = -V_{C2} \\

C_1 \frac{dv_{C1}}{dt} = i_{L1} - i_{PN}; & C_2 \frac{dv_{C2}}{dt} = i_{L2} - i_{PN}

\end{cases}$$

(3)

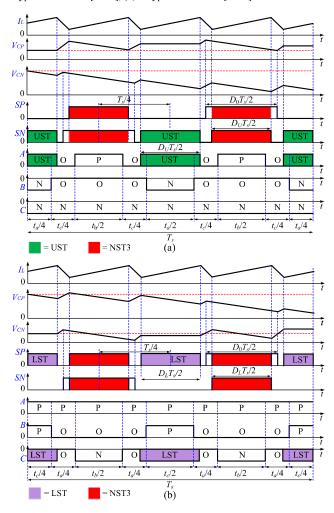

#### 2.2. Proposed DPWM Control Strategy

To reduce the switching commutation, the proposed method uses a DPWM strategy to generate the control signals to inverter switches. To detail this modulation method, let us first define three signals  $v_X$  (X = A, B, and C) as follows:

$$\begin{cases} v_A = 1/\sqrt{3} \times M \times \sin(2\pi f_o t) \\ v_B = 1/\sqrt{3} \times M \times \sin(2\pi f_o t - 2\pi/3) \\ v_B = 1/\sqrt{3} \times M \times \sin(2\pi f_o t - 2\pi/3) \\ M < 1 \end{cases}$$

$$(4)$$

where M is modulation index;  $f_0$  is fundamental frequency.

Three reference signals  $v_X^*$  (X = A, B, C), as shown in Figure 3, can be obtained by subtracting  $v_X$  from minimum value of  $v_A$ ,  $v_B$ ,  $v_C$  as follow:

$$v_X^* = v_X - \min(v_A, v_B, v_C) \tag{5}$$

Energies 2022, 15, 4889 5 of 18

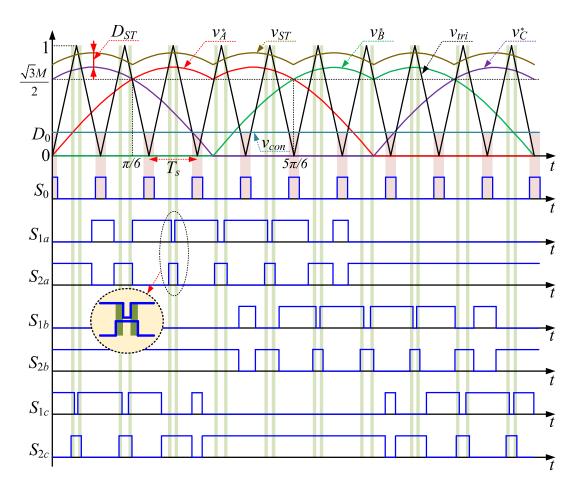

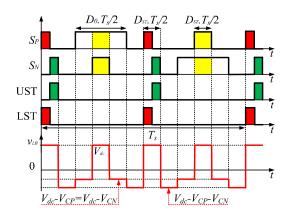

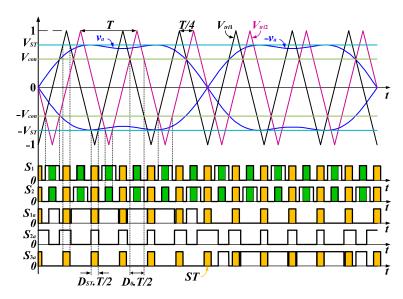

Figure 3. Proposed DPWM for introduced inverter.

These three reference signals are compared to high-frequency carrier  $V_{tri}$  like a conventional two-level inverter, to produce on/off switching signals for inverter side switches. In this scheme, one-third of the output period has no switching commutation in any phase leg, as shown in Figure 3. Thus, the switching loss can be reduced when compared to the conventional sinusoidal PWM method.

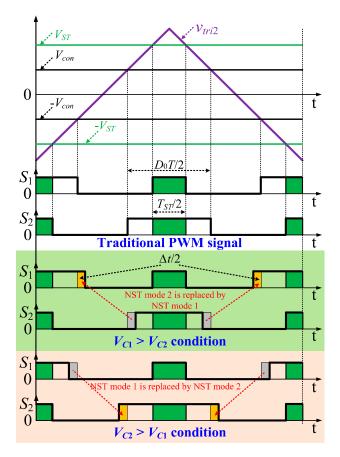

In the conventional PWM control method for single-stage inverters, the constant signal is used to generate the ST signal of the inverter leg. When this ST signal is inserted into the switching sequence, it produces at least two extra commutations in any phase leg. To overcome this, the proposed method uses discontinuous modulation signal  $v_{ST}$  and the maximum value of  $v_X^*$  to produce ST signal, as presented in Figure 3. In more detail, the ST signal is activated when  $\max(v_A^*, v_B^*, v_C^*) \leq V_{tri} \leq v_{ST}$ . Then, this ST signal is inserted into the phase which has the maximum value of reference signal  $v_X^*$  by triggering on both switches  $S_{1X}$  and  $S_{2X}$  of that phase leg. In this way, the ST insertion does not generate any extra switching commutation compared to conventional two-level VSI. For example, as shown in zoom-in waveforms of switches  $S_{1A}$  and  $S_{2A}$  control signals, there are only two switching commutations for each switch, which equals the conventional two-level inverter.

Like any impedance source two-level inverter, the ST state must be inserted within zero vectors. Therefore, ST duty ratio  $D_{ST}$  is not larger than (1 - M) and can be controlled independently by M. The  $v_{ST}$  signal and ST duty ratio are expressed as follows:

$$\begin{cases} v_{ST} = \max(v_A^*, v_B^*, v_C^*) + D_{ST} \\ D_{ST} \le 1 - M \end{cases}$$

(6)

where  $D_{ST}$  is ST duty ratio.

Energies 2022, 15, 4889 6 of 18

The control signal of  $S_0$  is generated by comparing control signal  $v_{con}$  to carrier signal  $V_{tri}$ , as shown in Figure 3. The  $v_{con}$  is identified as:

$$v_{con} = D_0 \tag{7}$$

where  $D_0$  is duty ratio of switch  $S_0$ .

In order not to affect the operating modes of the inverter,  $v_{con}$  must be satisfied with the following term:

$$v_{con} \le \sqrt{3}M/2 \Leftrightarrow D_0 \le \sqrt{3}M/2$$

(8)

#### 2.3. Steady-State Analysis

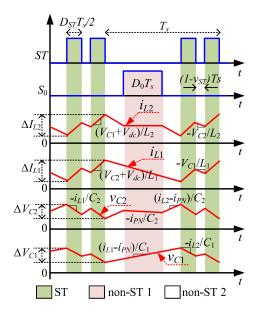

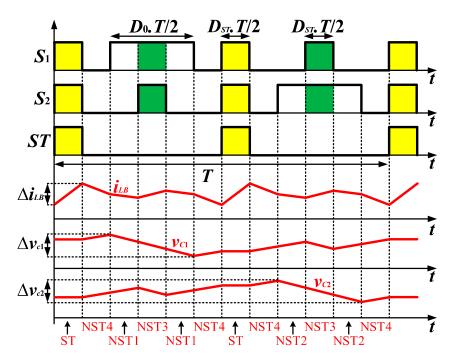

Figure 4 shows the profiles of inductor currents and capacitor voltages under one switching period,  $T_s$ . It is clear that the total time of ST mode is  $D_{ST} \cdot T_s$  for any period  $T_s$ . The time interval of non-ST mode 1 is equal to the on-time of switch  $S_0$  which is determined as  $D_0 \cdot T_s$ . The rest time of  $T_s$  is  $(1 - D_{ST} - D_0) \cdot T_s$ , which is the time interval of non-ST mode 2. By applying the volt-second balanced principle to two inductors,  $L_1$  and  $L_2$ , the capacitor and DC link voltages can be identified as:

$$\begin{cases} V_{C1} = V_{dc}(1 - D_0)D_{ST}/(1 - D_0 - 2D_{ST} + D_0D_{ST}) \\ V_{C2} = V_{dc}D_{ST}/(1 - D_0 - 2D_{ST} + D_0D_{ST}) \\ V_{PN} = V_{dc}(1 - D_0)/(1 - D_0 - 2D_{ST} + D_0D_{ST}) \end{cases}$$

(9)

Figure 4. Inductor currents and capacitor voltages in one switching period.

Assuming that the equivalent inverter current,  $i_{PN}$ , is constant, the average values of inductor currents can be approximately calculated by applying capacitor charge-balanced principle to capacitor  $C_1$  and  $C_2$  currents, as follows:

$$\begin{cases}

I_{L1} = i_{PN}(1 - D_0)(1 - D_{ST})/(1 - D_0 - 2D_{ST} + D_0D_{ST}) \\

I_{L2} = i_{PN}(1 - D_{ST})/(1 - D_0 - 2D_{ST} + D_0D_{ST})

\end{cases}$$

(10)

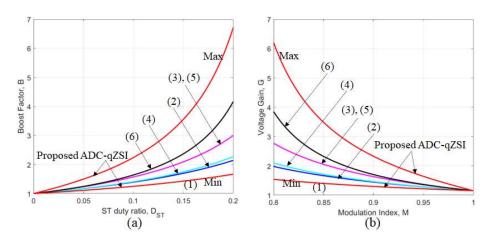

The boost factor, *B*, of the inverter is identified as:

$$B = \frac{V_{PN}}{V_{dc}} = \frac{1 - D_0}{1 - D_0 - 2D_{ST} + D_0 D_{ST}}$$

(11)

Energies 2022, 15, 4889 7 of 18

The peak value of fundamental component of output phase voltage is calculated as:

$$\hat{v}_X = 1/\sqrt{3} \times M \times V_{PN} \tag{12}$$

where  $\hat{v}_X$  is the peak value of output phase voltage.

The voltage gain, *G*, of proposed inverter is expressed as:

$$G = \frac{\hat{\sigma}_X}{V_{dc}/2} = \frac{2}{\sqrt{3}} \times \frac{M \times (1 - D_0)}{1 - D_0 - 2D_{ST} + D_0 D_{ST}}$$

(13)

By setting  $D_0$  to max value which is expressed in (8), the max voltage gain can be obtained.

#### 3. Parameter Selection

#### 3.1. Inductor and Capacitor Selection

As shown in Figure 4, the inductor current ripples are depended on the time interval of non-ST mode 2,  $(1 - v_{ST})T_s$ . When  $v_{ST}$  is maximum, the inductor current ripple is maximum. Based on (4)–(6), the maximum value of  $v_{ST}$  can be calculated as:

$$v_{ST,\max} = M + D_{ST} \tag{14}$$

Based on (1)–(3) and (14), the maximum value of inductor current ripples can be expressed as:

$$\begin{cases}

\Delta I_{L1} = V_{dc} M (1 - D_0) / (K L_1 f_s) \\

\Delta I_{L2} = V_{dc} D_{ST} (M - D_0) / (K L_2 f_s) \\

K = 1 - D_0 - 2D_{ST} + D_0 D_{ST}

\end{cases}$$

(15)

where  $\Delta I_{Lj}$  (j = 1, 2) is inductor  $L_j$  current ripple;  $f_s = 1/T_s$  is switching frequency.

$$\begin{cases}

\Delta V_{C1} = i_{PN} M D_{ST} / (K C_1 f_s) \\

\Delta V_{C2} = i_{PN} [M D_{ST} - (K - D_{ST}) D_0] / (K C_2 f_s)

\end{cases}$$

(16)

Based on (9), (10), (15) and (16), the inductors and capacitors are selected in terms of  $\Delta I_{Lj}/I_{Lj} \le k_1$ %, and  $\Delta V_{Cj}/V_{Cj} \le k_2$ %, where  $k_1$ % and  $k_2$ % are max acceptable ratios of inductor current and capacitor voltage ripples, respectively.

#### 3.2. Semiconductor Device Selection

The maximum reversed voltage of diode  $D_1$  is DC-link voltage, which is obtained in ST mode. The max reversed voltage of diode  $D_2$  equals the capacitor  $C_2$  voltage, which is achieved in non-ST mode 1.

The maximum value of diode  $D_2$  current is equal to the maximum value of inductor  $L_2$  current, which is obtained in non-ST mode 2, while the current through diode  $D_1$  achieves its maximum value in non-ST modes, which is calculated as:

$$\begin{cases} i_{D1,\text{max}} = i_{L1,\text{max}} + i_{L2,\text{max}} - i_{PN} \\ i_{Lj,\text{max}} = I_{Lj} + \Delta I_{Lj}/2 \text{ where } j = 1,2 \end{cases}$$

(17)

where  $i_{Lj,max}$  is the maximum value of inductor  $L_j$  current, which can be calculated by applying (10) and (15).

Switch  $S_0$  is only installed to transfer the energy of inductor  $L_2$ , and its current is constant when it is turned on, as shown in Figure 4. Thus, its current is the average value of the inductor  $L_2$  current, which is expressed in (10). As shown in (9), the voltage across  $S_0$  equals the voltage across capacitor  $C_2$ .

The voltage across the inverter side switches is equal to the DC link voltage. The maximum current through switch  $S_{1X}$  is ST current, which is determined by summing two max values of two-inductor currents.

Energies 2022, 15, 4889 8 of 18

#### 4. Semiconductor Loss Contribution

The power loss of semiconductor devices is classified into two groups: (1) loss of semiconductor devices of an impedance source circuit, and (2) power loss of inverter side switches. MOSFET devices are adopted for switching devices in this analysis.

#### 4.1. Loss of Switching Devices of Impedance-Source Network